Front end of line

The front-end-of-line (FEOL) is the first portion of IC fabrication where the individual devices (transistors, capacitors, resistors, etc.) are patterned in the semiconductor.[1] FEOL generally covers everything up to (but not including) the deposition of metal interconnect layers.

.svg.png.webp)

BEOL (metalization layer) and FEOL (devices).

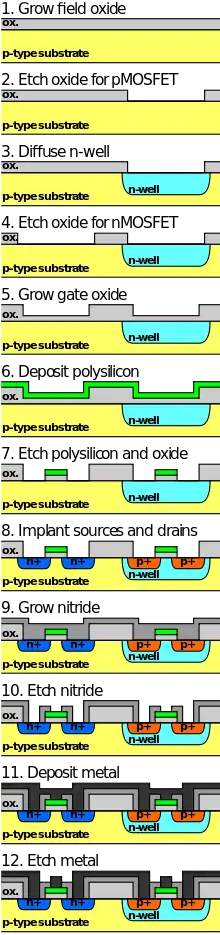

CMOS fabrication process

For the CMOS process, FEOL contains all fabrication steps needed to form fully isolated CMOS elements:

- Selecting the type of wafer to be used; Chemical-mechanical planarization and cleaning of the wafer.

- Shallow trench isolation (STI) (or LOCOS in early processes, with feature size > 0.25 μm)

- Well formation

- Gate module formation

- Source and drain module formation

See also

References

- Karen A. Reinhardt and Werner Kern (2008). Handbook of Silicon Wafer Cleaning Technology (2nd ed.). William Andrew. p. 202. ISBN 978-0-8155-1554-8.

Further reading

- "CMOS: Circuit Design, Layout, and Simulation" Wiley-IEEE, 2010. ISBN 978-0-470-88132-3. pages 177-178 (Chapter 7.2 CMOS Process Integration); pages 180-199 (7.2.1 Frontend-of-the-line integration)

This article is issued from Wikipedia. The text is licensed under Creative Commons - Attribution - Sharealike. Additional terms may apply for the media files.